Product Summary

The Spartan-3 XC3S200-4FTG25 Field-Programmable Gate Array is specifically designed to meet the needs of high volume, cost-sensitive consumer electronic applications. The XC3S200-4FTG25 offers densities ranging from 50,000 to five million system gates, as shown in Table 1. The Spartan-3 XC3S200-4FTG25 builds on the success of the earlier Spartan-IIE family by increasing the amount of logic resources, the capacity of internal RAM, the total number of I/Os, and the overall level of performance as well as by improving clock management functions. Numerous enhancements derive from state-of-the-art Virtex-II technology. These Spartan-3 enhancements, combined with advanced process technology, deliver more functionality and bandwidth per dollar than was previously possible, setting new standards in the programmable logic industry. Because of their exceptionally low cost, Spartan-3 FPGA XC3S200-4FTG25 is ideally suited to a wide range of consumer electronics applications, including broadband access, home networking, display/projection and digital television equipment.

Parametrics

XC3S200-4FTG25 absolute maximum ratings: (1)VCCINT Internal supply voltage: –0.5 to 1.32 V; (2)VCCAUX Auxiliary supply voltage: –0.5 to 3.00 V; (3)VCCO Output driver supply voltage: –0.5 to 3.75 V; (4)VREF Input reference voltage: –0.5 to VCCO+0.5 V; (5)VIN Voltage applied to all User I/O pins and Dual-Purpose pins, Driver in a high-impedance state: –0.5 to VCCO+0.5 V; (6)Voltage applied to all Dedicated pins: –0.5 to VCCAUX+0.5 V; (7)TJ Junction temperature, VCCO ≤ 3.0V: 125 ℃; VCCO > 3.0V: 105 ℃; (8)TSOL Soldering temperature: 220 ℃; (9)TSTG Storage temperature: –65 to 150 ℃.

Features

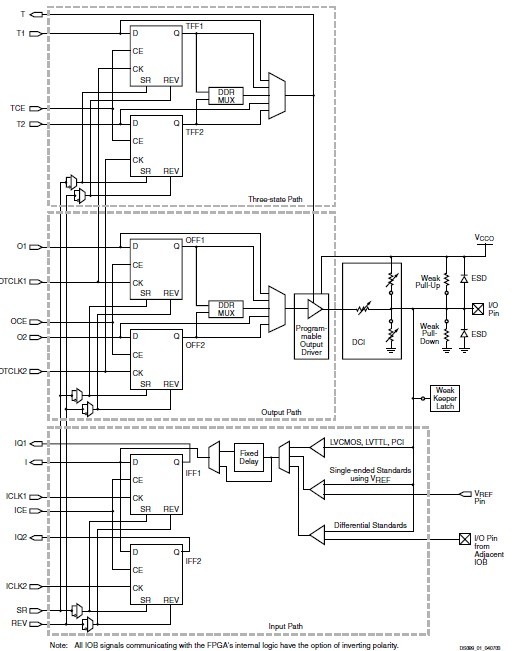

XC3S200-4FTG25 features: (1)Revolutionary 90-nanometer process technology; (2)Very low cost, high-performance logic solution for high-volume, consumer-oriented applications; (3)Densities as high as 74,880 logic cells; (4)326 MHz system clock rate; (5)Three power rails: for core (1.2V), I/Os (1.2V to 3.3V), and auxiliary purposes (2.5V); (6)Up to 784 I/O pins; (7)622 Mb/s data transfer rate per I/O; (8)Seventeen single-ended signal standards; (9)Seven differential signal standards including LVDS; (10)Termination by Digitally Controlled Impedance; (11)Signal swing ranging from 1.14V to 3.45V; (12)Double Data Rate (DDR) support; (13)Abundant logic cells with shift register capability; (14)Wide multiplexers; (15)Fast look-ahead carry logic; (16)Dedicated 18 x 18 multipliers; (17)JTAG logic compatible with IEEE 1149.1/1532 specifications; (18)SelectRAM hierarchical memory; (19)Up to 1,872 Kbits of total block RAM; (20)Up to 520 Kbits of total distributed RAM; (21)Digital Clock Manager (up to four DCMs); (22)Clock skew elimination; (23)Frequency synthesis; (24)High resolution phase shifting; (25)Eight global clock lines and abundant routing; (26)Fully supported by Xilinx ISE development system; (27)Synthesis, mapping, placement and routing; (28)MicroBlaze processor, PCI, and other cores.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

XC3S200-4FTG256C |

|

IC SPARTAN-3 FPGA 200K 256-FTBGA |

Data Sheet |

|

|

||||||||||

|

XC3S200-4FTG256I |

|

SPARTAN3A FPGA 200K STD 256FTBGA |

Data Sheet |

|

|

||||||||||

(United Kingdom)

(United Kingdom)